This is not an ADB material. The views expressed in this document are the views of the author/s and/or their organizations and do not necessarily reflect the views or policies of the Asian Development Bank, or its Board of Governors, or the governments they represent. ADB does not guarantee the accuracy and/or completeness of the material's contents, and accepts no responsibility for any direct or indirect consequence of their use or reliance, whether wholly or partially. Please feel free to contact the authors directly should you have queries.

# IC Design Research & Development in Institut Teknologi Bandung

Prof. Trio Adiono, PhD

University Center of Excellence on Microelectronics Institut Teknologi Bandung

# Competency in IC Design

Full Custom Design (Analog & Mixed Signal)

Schematic Design

**Design Simulation**

Floorplaning and Placement and Routing

Semi Custom

Hardware Design Modeling

Architecture Design

RTL Design & Simulation

System On Chip

Hardware & Software Co Design

IP Design

Integration of in-house IP, third party IP and foundry IP in SoC development

Peancangan Sistem VLSI

# Competency in Chip Design

- ASIC Front-End Design & Verification

- Design Synthesis

- Simulation (Functional, Gate and Full Timing)

- Static Timing Analysis

- ASIC Back-End Design & Verification

- Formal Verification

- Static Timing Analysis

- Floorplanning

- Physical P&R

- DRC/LVS

- Parasitic Extraction

- Crosstalk/IR Drop

- Design-For-Test

- Memory, Functional BIST

- SCAN Insertion/ ATPG

- JTAG

- System Verification Planning

- Verilog/SystemC

- Directed Test and Assertion Based

- FPGA Prototyping

- Design Synthesis and Optimization

- In Circuit Verification

# RESEARCH & DEVELOPMENT

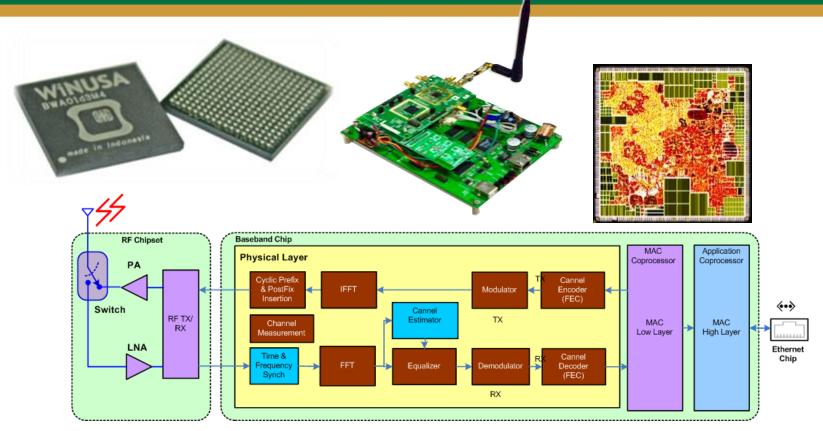

# Chip: Baseband Processor

# Measurements/Prototyping

ınfınıte Be

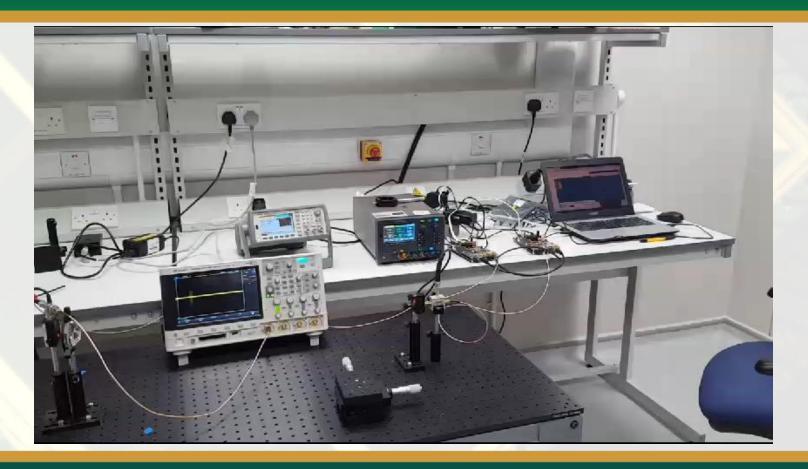

# Real-time Prototype

# Mashed Network Wireless Communications

# Real-Time Performance Measurement (RED LED)

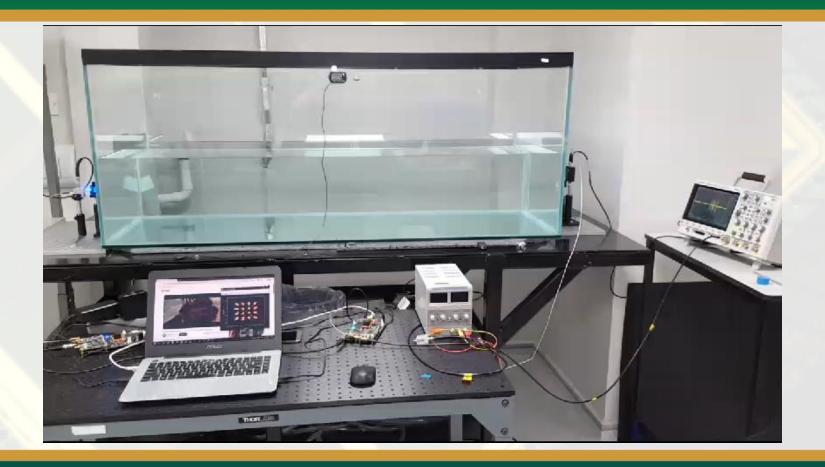

# Real-Time Under Water Communication

# NEAR FIELD COMMUNICATION

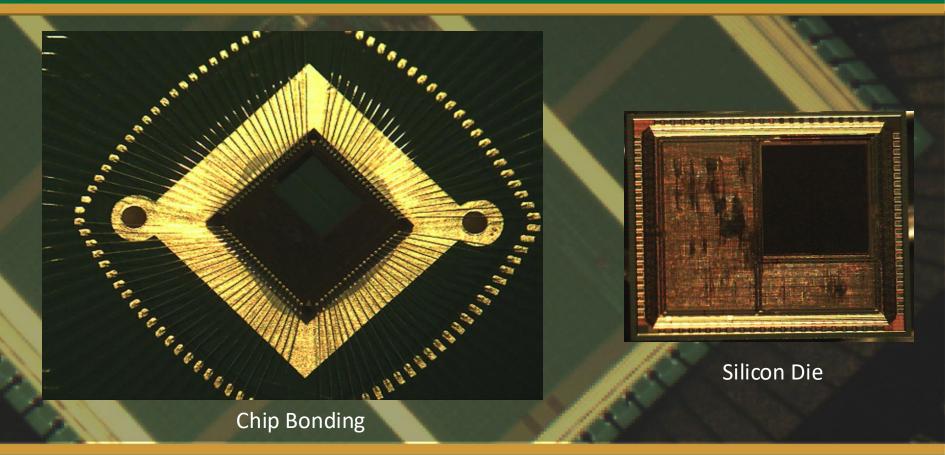

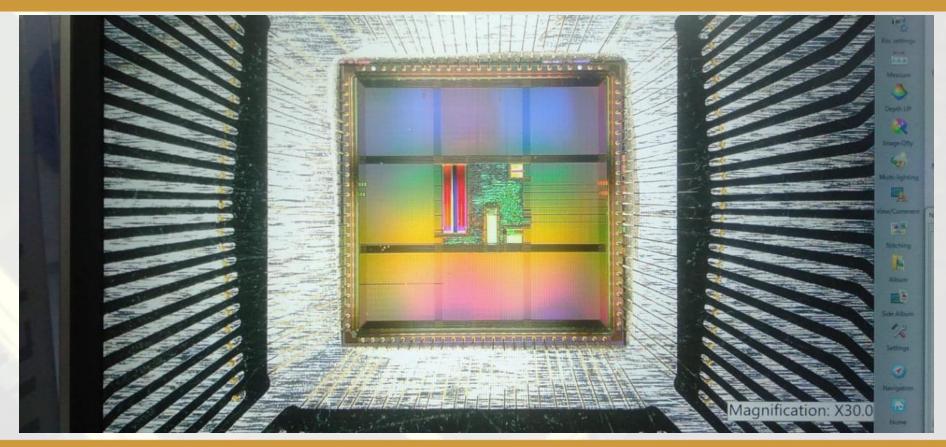

# NFC Chip Silicon Dies

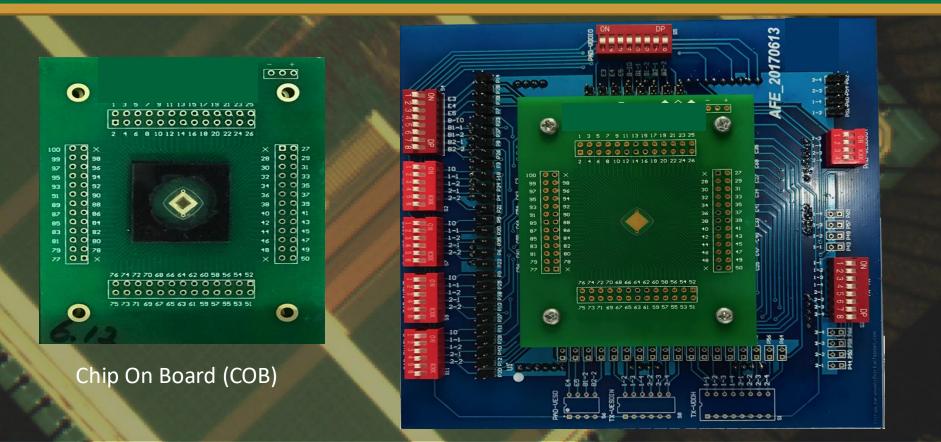

# Chip Testboard & CoB

# NFC Communication

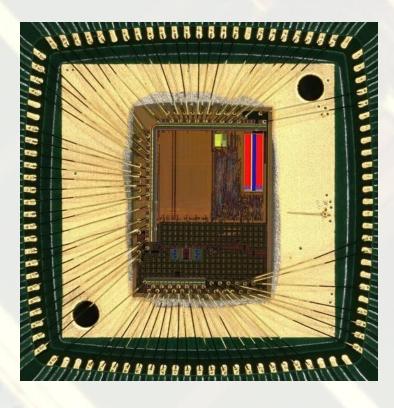

# Analog Design Layout PLL

Foto mikroskopik dari *chip* osilator terkendali yang dimuat di atas *Circuit-on-Board*.

# Artificial Intelligence Research

### Supervised Learning

### Low Latency YOLOv3-Tiny Accelerator for Low-Cost FPGA Using General Matrix Multiplication Principle

TRIO ADIONO<sup>©1,2</sup>, (Member, IEEE), ADIWENA PUTRA<sup>©2</sup>, NANA SUTISNA<sup>©1,2</sup>, (Member, IEEE), INFALL SYAFALNI<sup>©1,2</sup>, (Member, IEEE), AND RAHMAT MULYAWAN<sup>©1,2</sup>, (Member, IEEE)

<sup>1</sup>Electrical Engineering Department, School of Electrical Engineering and Informatics, Institut Teknologi Bandung, Bandung, West Java 40116, Indonesia <sup>2</sup>University Center of Excellence on Microelectronics, Institut Teknologi Bandung, Bandung, West Java 40132, Indonesia

EE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION AVISIN SYSTEM

### Fast and Scalable Multicore YOLOv3-Tiny Accelerator Using Input Stationary Systolic Architecture

Trio Adiono<sup>®</sup>, Senior Member, IEEE, Rhesa Muhammad Ramadhan<sup>®</sup>, Student Member, IEEE, Nana Sutisna<sup>®</sup>, Member, IEEE, Infall Syafalni<sup>®</sup>, Member, IEEE, Rahmat Mulyawan<sup>®</sup>, Member, IEEE, and Chang-Hong Lin<sup>®</sup>, Member, IEEE

### **Unsupervised Learning**

# FARANE-Q: Fast Parallel and Pipeline Q-Learning Accelerator for Configurable Reinforcement Learning SoC

NANA SUTISNA<sup>1,2</sup>, (Member, IEEE), ANDI M. RIYADHUS ILMY<sup>1</sup>, INFALL SYAFALNI<sup>©1,2</sup>, (Member, IEEE), RAHMAT MULYAWAN<sup>©1,2</sup>, (Member, IEEE), AND TRIO ADIONO<sup>©1,2</sup>, (Senior Member, IEEE)

<sup>1</sup>School of Electrical Engineering and Informatics, Institut Teknologi Bandung, Bandung, West Java 40132, Indonesia

<sup>2</sup>University Center of Excellence on Microelectronics, Institut Teknologi Bandung, Bandung, West Java 40132, Indonesia

### Security

# Efficient Homomorphic Encryption Accelerator With Integrated PRNG Using Low-Cost FPGA

Publisher: IEEE

Cite This

Infall Syafalni 🗓 ; Gilbert Jonatan ; Nana Sutisna 🗓 ; Rahmat Mulyawan 🗓... All Authors

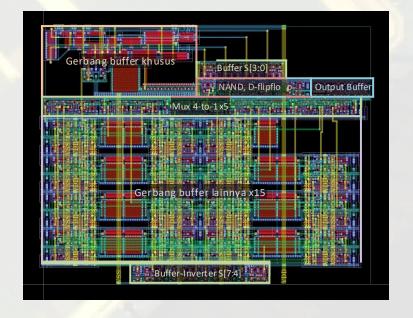

# Artificial Intelligence Chip

Lab IC Desain

Pusat Mikroelektronika ITB

# Modul Sensor

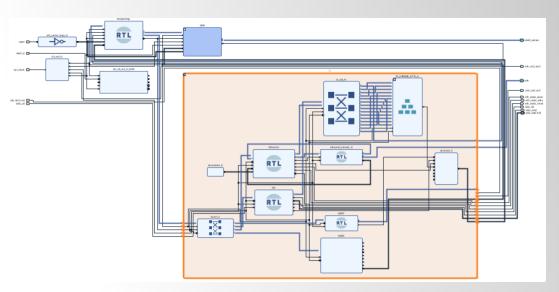

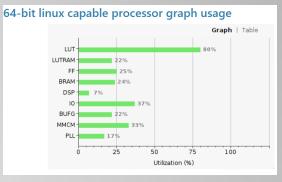

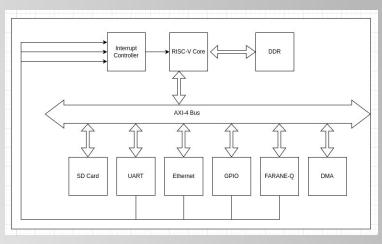

# **RISCV+AI Accelerator**

### Hardware: RISC-V Softcore to FARANE-Q Implementation

# 32-bit embedded processor graph usage Graph | Table LUTLUTRAM 20% FF 20% BRAM 24% DSP 1% IO 37% BUFG 22% MMCM 33%

75

Utilization (%)

100

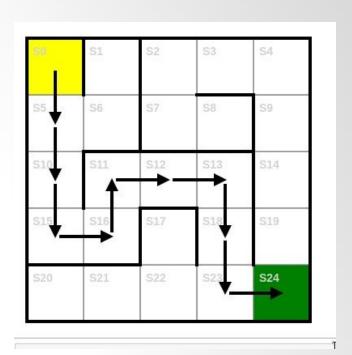

# Reinforcement Learning

Software: PYNQ's Jupyter-notebook to C conversion

```

| 110 : 4 | 11 : 4 | 12 : | 113 : | 114 : | 1 | 115 : 4 | 16 : + | 17 : | 118 : | 119 : | 1 | 1110 : 4 | 1111 : + | 112 : + | 113 : 4 | 114 : | 1 | 1115 : + | 116 : + | 117 : | 1118 : 4 | 119 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1121 : | 1122 : + | 1123 : + | 1124 : | 1 | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 : | 1120 :

```

# INDUSTRIAL COLLABORATION

# **Energy Meter**

**Smart Energy Meter**

DLMS Energy Meter Modem

# Internet Of Things (IoT)

# Medical : Smart Pump

### **Syringe Pump**

### **Infusion Pump**

# Medical: Cardio

**Patient Monitor**

# **Medical: Spirometer**

Direct contact with patients using temperature sensors, SPO2, and respiratory sensors (mouthpiece).

Android & IOS App

### **Awards**

- LSI Design Contest, 2014, Japan, 1<sup>st</sup> Winner, "Smart Info Media (SIS) Award".

- 1st Award (SIS Award), 2009 LSI Design Contest, Okinawa

- 3th Award (Xilinx Award), 2009 LSI Design Contest, Okinawa

- Asia Pacific Information Technology Award (APICTA) 2008

- IEICE, Communication Society Award, 2008 LSI Design Contest, Okinawa

- Semiconductor Industry News Paper Award, 2008 LSI Design Contest, Okinawa

- The Best Feature Award, 2007 LSI Design Contest, Okinawa

- The Best Feature Award, 2006 LSI Design Contest, Okinawa

# nnovation Park Bandung Teknopolis

# Smart Industry Creative Center Focus on Industry 4.0

Artificial Intelligence, Internet of Things, Virtual Reality, 5G, and Big Data

### **Urgency of Development:**

- Provision and management of clean laboratories for Industry

Innovation products

- 2. Facilities for innovation research activities to produce

As part of Major Project National Perpres No.18/2020, start of construction in 2021-

| Building Name         | Number of<br>Floors   | Building Area (m2)                                   |

|-----------------------|-----------------------|------------------------------------------------------|

| 1st Building          | 13                    | 18.099                                               |

| 2nd Building          | 12                    | 12.038                                               |

| 3rd Building          | 11                    | 8.815                                                |

| 4th Building          | 11                    | 2.720                                                |

| TO                    | ΤΛΙ                   | 11 551                                               |

| Building              | Building Area<br>(m2) | Status                                               |

| 1st & 2nd<br>Building | 6.027                 | Has been granted<br>and received land<br>certificate |

|                       |                       | Land grants in                                       |

| 3rd & 4th             | 3.873                 | 2023 according to<br>the progress of                 |

### Bandung Teknopolis | Mapping Plan for pment Support and Industrial Innovation Research

### **Building 2**

Equipment Procurement Cost : USD 2.788.580

**Building 3**

### 11th Floor (930m2) Computed Tomography

7th Floor (675m2) Defense & Security

10th Floor (1130 m 2) EMC Testing, Battery

Testing & Electric Compon pents Bench Testing

6 & 5 th (1350m2) Incubator & Accelerator

Ground Floor (150m2) **Dynotest Facilities**

### **Masterplan Design**

### **Building 1**

Equipment Procurement Cost : USD 4.748.122

11th Floor (1.465 m2) Stem Cell & Eksosom Lab

10th Floor (1.465 m2)

8th Floor (1.456 m2)

6th Floor (1.456 m2)

PCB Tech & IC Design

Center

3 & 4th Floor

(2.8108 m2)

Center &

Catalyst & Anchor

Industry Research

Commercial Area

**Bioinformatics Lab**

Transportation & Vehicle

Radar & Technopark

Dormitory

9th Floor (1.465 m2) Smart City & Command

12-13th Floor (2.565 m2

7th Floor (1.456 m2)

m2)

Mini Wafer

Fabrication

GF & Public Outdoor

### **Building 4**

4 & 5 Floor (1700 m2) Anchor Industry.

GF. 1 & 2 Floor (1700 m2) Function Hall & Commercial Area

7 & 6th Floor (1930 m2) Open Innovation Lab.

9-10 Floor (1980m2)

8th Floor (990 m2)

Digital Security &

Cyber Physical Syster

10 & 11th Floor (900m2 Co-Working Spaces

4 & 5th Floor (1100 m2) Incubator & Accelerator

9th Floor (600 m2) Additive Manufacturing Lab

2 & 3rd Floor (1100 m2) Commercial Area. Café & Lounge

Forensics

Microelectronics Center www.pme.itb.ac.id | info@pme.itb.ac.id

## **International University Networks**

- Tokyo Institute of Technology, Japan

- Shibaura Institute of Technology, Japan

- Keio University, Japan

- University of Twente, Netherlands, SPIN Mobility Program

- NNTTF (National Networked Tele Test Facility for Integrated System)-Australia

- University Sains Malaysia, Malaysia

- Kyushu Institute of Technology, Japan

- Kumoh National Institute of Technology, Korea

- Japan Advance Institute of Technology, JAIST

- Pukyong Nationbal University, Korea

- Eidenburg, UK

- National Taiwan University of Science and Technology

- Korea Advance Institute of Science and Technology

★ Tokyo Institute of Technology

芝浦工業大學

SHIBAURA INSTITUTE OF TECHNOLOGY

한국과학기술원

unec